### WAFER-SCALE LASER PANTOGRAPHY: IV. PHYSICS OF DIRECT LASER-WRITING MICRON-DIMENSION TRANSISTORS

IRVING P. HERMAN, BRUCE M. MCWILLIAMS, FRED MITLITSKY, HON WAH CHIN, RODERICK A. HYDE and LOWELL L. WOOD

Lawrence Livermore National Laboratory, P.O. Box 808, Livermore, CA 94550, USA

#### ABSTRACT

The processes involved in the fabrication of micron-dimension transistors and small-scale integrated circuits using only the technique of direct laser-writing by localized pyrolytic surface reactions are discussed. New experimental findings in the deposition of tungsten by silicor, surface reduction of tungsten hexafluoride and doped polysilicon are presented. The techniques used to fabricate laser beam-written n-MOSFET's are being extended to make unipolar JFET's and bipolar lateral pnp transistors.

# INTRODUCTION

We recently reported<sup>[1]</sup> the ab initio fabrication of functional n-MOS field-effect transistors on a silicon wafer using only local laser-induced pyrolytic deposition, doping and etching reactions to effect the required semiconductor surface patterning. The laser pantographic techniques demonstrated in Ref. 1 can be readily applied to the fabrication of other unipolar (JFET) and also bipolar (lateral, vertical) transistors, to the repair of non-functioning units of complex integrated circuits, and to the multilayer interconnection of integrated circuit devices. Indeed, one subset of the latter capability was recently demonstrated<sup>[2]</sup> in the single layer interconnection of a CMOS gate array with laser beam-deposited doped polysilicon.

With control of the laser writing processes sufficient to optimize device quality and creation speed, these device fabrication, interconnection and repair techniques can be combined to usher in an era of rapid, high yield, discretionary fabrication of very complex circuits, such as customized supercomputers, on a single wafer. Clearly, timely attainment of such challenging goals requires a sufficient set of well-characterized and compatible direct laser beam-writing technologies. Several of those used to fabricate n-MOSFET's are further examined here. We are also currently using these laser direct-writing techniques to fabricate JFET's and bipolar lateral pnp transistors.

A sufficient set of laser processing steps for creating silicon-based unipolar and bipolar devices includes (selective) etching/deposition of insulators (SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>) for MOS gates and interconnect isolation; deposition (and etching) of doped polysilicon or doping pre-deposited silicon for gates, doped regions and interconnects for both unipolar and bipolar devices; and deposition of metals and metal silicides for interconnects and gates (W, WSi<sub>2</sub>, Mo, Al, Au). Several of these steps have been demonstrated, such as etching of Si or SiO<sub>2</sub> with added HCl<sup>[1,3]</sup> or Cl<sub>2</sub><sup>[3]</sup> or, at times, in vacuum;<sup>[1]</sup> deposition of doped polysilicon with silane<sup>[1,4,5]</sup> laced with dopants (PH<sub>3</sub>, B<sub>2</sub>H<sub>6</sub>),<sup>[1]</sup> and deposition of metal microstructures such as W (using WF<sub>6</sub> + H<sub>2</sub>),<sup>[1,6]</sup> Ni (from Ni(CO)<sub>4</sub>),<sup>[7,8]</sup> Al (from Al(CH<sub>3</sub>)<sub>5</sub>),<sup>[6]</sup> etc. Still, much needs to be learned about the electrical, structural, and adhesion properties of these (and other) laser beam-induced semiconductor modification processes.

In the laser beam-driven fabrication of n-MOSFETs,<sup>[1]</sup> a silicon wafer surfaced with a thermally grown silicon dioxide film was used as the input substrate. The focused laser locally milled away the oxide layer (and sometimes purposely some of the underlying silicon) to pattern device source and drain regions, thereby demonstrating the compatibility of direct laser beam-writing with non-local processing.

Tungsten<sup>[10]</sup> and tungsten silicide<sup>[11]</sup> are very promising interconnect materials for next-generation VLSI/ULSI circuitry. The advantages of tungsten silicide include its low resistivity (compared to doped polysilicon), its high resistance to electromigration (compared to aluminum), and its ability to form a stable oxide. Pure tungsten has even better resistivity and electromigration properties than does tungsten silicide, though its oxide has poorer qualities. Consequently, laser-initiated deposition of W and WSi<sub>2</sub> are expected to be highly useful laser pantographic techniques, and deserving of further study.

Tungsten microstructures have previously been fabricated by hydrogen reduction of tungsten hexafluoride<sup>[1,6]</sup> on a laser-heated substrate:

$$WF_6 + 3H_2 \rightarrow W(s) + 6HF - 13 \text{ Kcal/mole} (1300 \text{ K})$$

(1)

An analogous process has been used to deposit tungsten on a non-locally heated silicon substrate<sup>[12,13]</sup> through reduction of WF<sub> $\theta$ </sub> by the silicon surface:

$$WF_{6} + \frac{3}{2}Si(s) \rightarrow W(s) + \frac{3}{2}SiF_{4} + 171 \text{ Kcal/mole (1300 K)}$$

(2)

This reaction is intrinsically self-aligning on silicon and should produce superior ohmic contacts with better adhesion than those produced by the  $WF_6/H_2$  reaction, since the WF<sub>6</sub> reacts with the atomically-bare silicon surface in reaction (2), while a tungsten deposit can also form on an impurity overlayer with reaction (1). With no added hydrogen, the thickness of the deposit, which is expected to be tungsten or tungsten silicide, is self-limited by the diffusion of WF<sub>6</sub> through the previously deposited molten or solid layers to fresh silicon surfaces. Thicker tungsten layers can then be made by adding hydrogen to the tungsten hexafluoride. The early results of a study of the formation of tungsten/silicon interfaces using local heating to drive the silicon reduction of tungsten hexafluoride are reported here.

As mentioned above, the deposition of doped polysilicon is an important step in many integrated circuit fabrication processes. A comprehensive study of the kinetics of the deposition of doped polysilicon and the electrical and materials properties of the deposit is underway. Some findings in the study of the deposition of phosphorous- and boron-doped silicon using  $PH_3/SiH_4$  and  $B_2H_6/SiH_4$ , respectively, are presented here.

The laser direct writing processes which are used to create MOSFET's are also useful in generating unipolar junction field effect transistors (JFET's) and bipolar transistors. Use of local laser pyrolytic reactions to realize JFET and bipolar transistors with micron-scale channel length/base width is also discussed here.

### EXPERIMENTAL APPARATUS

The laser microscope and overall experimental assembly in the present work are similar to those used in previous studies (Ref. 1, Figure 1; Ref. 7, Figure 2); the process-oriented microscope permits direct viewing of the vacuum chamberpositioned semiconductor substrate by a vidicon, and simultaneous irradiation by the laser beam focused onto the substrate. As in previous work, laser pulses are formed by electro-optically modulating the output of a CW argon-ion laser tuned to 5145 Å. These pulse sequences are coordinated with the x-y motion of the wafercontaining reaction chamber by computer control.

## EXPERIMENTAL PROCEDURE AND RESULTS

#### Laser-Deposited Tungsten

In the tungsten deposition experiments, WF<sub>6</sub> at 100-1000 Torr pressures was introduced into a vacuum cell with a p-type (100), 40  $\Omega$ -cm silicon substrate that was degreased by solvents and treated with buffered HF to remove the native oxide layer. In the base case experiment, the wafer was mechanically scanned and the laser was electro-optically pulsed to give a single incident 100  $\mu$ sec pulse for each sub-micron increment of wafer travel. The 5145 Å radiation incident on the target was focused by a 20x, N.A.=0.4 objective to a spot diameter ~2  $\mu$ m.

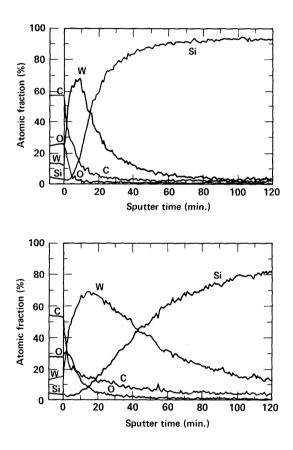

The tungsten pads so deposited appeared shiny and much more reflective than the bare silicon substrate. Lines drawn under these conditions had widths  $\lesssim 1 \ \mu$ m, as determined by scanning electron microscopy. Auger analysis was performed on the pads after various stages of sputtering. No fluorine ( $\lesssim 1\%$ ) from the WF<sub>6</sub> was seen in any case examined. Small amounts of carbon and oxygen were observed near the surface, ascribed to handling and SEM analysis. As seen in Figure 1 (top) for the base case, the average thickness of the tungsten overlayer was ~180 Å (defined as the depth at which the tungsten atomic concentration is half the surface maximum). The Auger profile obtained with a total of two to five laser-overwriting scans on the same pad are essentially the same as with a single scan. Similar Auger profiles were observed with hydrogen added to the reaction gas mixture.

A significantly thicker tungsten deposit (~550 Å) in neat WF<sub>0</sub> was obtained when the laser pulse duration was increased to 500  $\mu$ sec, as seen in Figure 1 (bottom). The surface layer in each case examined is apparently pure W with no contribution from tungsten silicide, WSi<sub>2</sub>. The observed W/Si depth profile is, in part, due to the diffusion of WF<sub>0</sub> and W in the Si and, in part, to surface non-uniformities in deposition.

#### Laser-Deposited Doped Polysilicon

The reaction gases used in the doped polysilicon deposition experiments were vendor-supplied 1% B<sub>2</sub>H<sub>6</sub>/SiH<sub>4</sub> and 1% PH<sub>3</sub>/SiH<sub>4</sub> mixtures, and samples further diluted in-house with silane. A thoroughly cleaned p-type (100), 6-9  $\Omega$ -cm silicon wafer with 1  $\mu$ m thick silicon dioxide overlayer was the target substrate. The laser was focused (20x objective) at the Si-SiO<sub>2</sub> interface and not at the SiO<sub>2</sub>-gas boundary. For resistivity measurements ~500  $\mu$ m long, ~8  $\mu$ m wide and ~1.5  $\mu$ m thick lines were made, with four probing pads deposited at points appropriate for current and voltage measurements. Each line consisted of two laser-scans over the substrate. The transverse profile of each line was measured by profilometry.

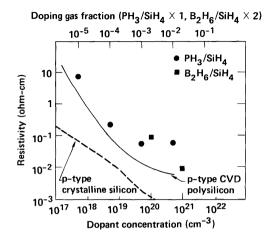

Preliminary resistivity data is shown in Figure 2, plotted as a function of the  $B_2H_6/PH_5$ -to-SiH<sub>4</sub> ratio (upper ordinate scale) and also the polysilicon dopant concentration assuming molecular stoichiometric deposition (lower ordinate scale). Published curves of the resistivity of bulk p-type (boron) crystalline silicon<sup>[14]</sup> and high temperature (985°C) CVD p-type (boron) polycrystalline (~1  $\mu$ m grain size)<sup>[15]</sup> vs. the boron concentration are displayed for reference. For phosphorus-doped material, the resistivity is nearly the same as for boron (~0.7× displayed crystalline value;<sup>[14]</sup> ~ same for polysilicon<sup>[16]</sup>). The resistivity of non-annealed silicon deposited by this (non-optimized) laser process is quite close to that of bulk CVD-deposited material.

SIMS analysis of these structures suggests that the P/Si doping ratio in the bulk of the deposited silicon pads using  $[PH_3]/[SiH_4] = 10^{-2}$  may be only ~3 times larger than using  $[PH_3]/[SiH_4] = 10^{-3}$ . This could explain the flattening of the resistivity data for the phosphorous-doped structures in Figure 2.

FIG. 1. Auger element analysis as a function of sputtering time for tungsten deposition from WF<sub>0</sub>/Si(s) reactions. In the top curve 100  $\mu$ sec long laser pulses were used (1 pulse per 0.1  $\mu$ m travel), while 500  $\mu$ sec pulses were used in the bottom curve. A sputter time of 10 minutes corresponds to removal of about 100 Å of material.

FIG. 2. Resistivity of laser-deposited doped polysilicion as a function of doping gas concentration  $(PH_3/SiH_4 \times 1, \text{ closed circles}; B_2H_6/SiH_4 \times 2, \text{ plotted as closed squares})$ . The lower ordinate axis converts this ratio to a silicon deposit doping level assuming equal rates of SiH<sub>4</sub>, PH<sub>3</sub> and B<sub>2</sub>H<sub>6</sub> surface decomposition. Also shown, are resistivity curves for p-type (boron) crystalline<sup>[14]</sup> (dashed line) and high-temperature CVD polycrystalline silicon<sup>[15]</sup> (solid line).

# JFET/LATERAL PNP TRANSISTORS

A silicon-on-sapphire wafer (0.5  $\mu$ m thick p-type Si, 3 × 10<sup>16</sup> B atoms/cc) was laser beam-etched entirely through the silicon layer in the presence of HCl gas in order to electrically isolate the several transistor regions. Phosphorous-doped polysilicon was deposited across the width of the p-type island to form the gate of the (depletion-mode) junction field-effect transistor. Lateral pnp transistors were fabricated as were the JFET's, with additional heating to drive the phosphorous dopants all the way through the silicon layer, or by filling a laser beam/HCl-scribed trough between the collector and emitter regions of the moat-circumscribed borondoped silicon regions with phosphorous-doped polysilicon. These procedures were sometimes followed by laser annealing of the entire base region.

Functional analysis of these devices is being performed.

### CONCLUSIONS

We have previously reported the ab initio creation of MOSFET transistors via laser beam-energized, pyrolytically mediated patterning of the surfaces of silicon surfaces, and the interconnection of several such transistors to realize small scale integrated (SSI) circuits. The present paper reports on studies of the process physics underlying these earlier results, along with current work which is resulting in the direct laser-write creation of unipolar/bipolar transistors of two basic types, all with micron-scale minimum feature sizes.

The ability to synthesize MOSFET, JFET and lateral bipolar transistors with the same laser pantographic processes and techniques indicates that creation of wafer-scale integrated circuits containing intimate mixes of these different types of active devices (e.g., bipolar device-implemented logic elements in close proximity to FET-implemented memory cells) will be straightforward. We expect that the laser beam-etched moat-and-island electrical isolation technique used in the bipolar transistor synthesis work, combined with the intrinsic advantages of shallow device structures created on insulating substrates, will prove to be a valuable and widely applicable approach in subsequent laser pantographic research.

### ACKNOWLEDGMENTS

The authors wish to thank Dr. J. Balch for doping the silicon-on-sapphire substrates, D. Duerre, E. Ormsby, L. R. Mendonca and W. F. Gee for expert technical assistance throughout this work, and J. Trevino and J. Fischer for assisting with sample preparation and analysis.

Work performed under the auspices of the U.S. Department of Energy by the Lawrence Livermore National Laboratory under Contract W-7405-Eng-48.

### REFERENCES

- B. M. McWilliams, I. P. Herman, F. Mitlitsky, R. A. Hyde, and L. L. Wood, Appl. Phys. Lett., 43, 946 (1983).

- H. W. Chin, B. M. McWilliams, F. Mitlitsky, J. C. Whitehead, and L. L. Wood, Wafer-Scale Laser Pantography V: Hour-Scale Start-to-Finish Interconnection of VLSI CMOS Gate Arrays, UCRL-89639 (1983). (To appear in summary in Proc. USDoE 1983 CAD Conference, Livermore CA, October 1983.)

- D. J. Ehrlich, R. M. Osgood Jr., and T. F. Deutsch, Appl. Phys. Lett., 38, 1018 (1981).

- D. J. Ehrlich, R. M. Osgood Jr., and T. F. Deutsch, Appl. Phys. Lett., 39, 957 (1981).

- D. Bäuerle, P. Irsigler, G. Leyendecker, H. Noll, and D. Wagner, Appl. Phys. Lett., 40, 819 (1982).

- 6. S. D. Allen and A. B. Tringubo, J. Appl. Phys., 54, 1641 (1983).

- I. P. Herman, R. A. Hyde, B. M. McWilliams, A. H. Weisberg, and L. L. Wood, Materials Research Society Symposia Proceedings (November 1982), 17, Laser Diagnostics and Photochemical Processing for Semiconductor Devices, edited by R. M. Osgood Jr, S. R. J. Brueck, and H. R. Schlossberg, (Elsevier, New York, 1983), p. 9.

- 8. W. Kräuter, D. Bäuerle, and F. Fimberger, Appl. Phys., A31, 13 (1983).

- 9. D. J. Ehrlich, R. M. Osgood Jr., and T. F. Deutsch, IEEE J. Quantum Electron., QE-16, 1233 (1980).

- 10. P. L. Shah, IEEE Trans. Electron. Devices, ED-26, 631 (1979).

- S. P. Muraka, Silicides for VLSI Applications, (Academic Press, New York, 1983), p. 2.

- T. Moriya, K. Yamada, T. Shibata, H. Iizuka and M. Kashiwagi, Proceedings of the Symposium on VLSI Technology, Hawaii, Sept. 12-14, 1983, Presentation 7-6 (IEEE, 1983).

- 13. J. M. Shaw and J. A. Amick, RCA Rev., 306 (1970).

- S. M. Sze, Physics of Semiconductor Devices, 2nd Edition (J. Wiley, New York, 1981), p. 32.

- J. J. Yang, W. I. Simpson, and R. P. Ruth, J. Electron. Mater., 10, 1011 (1981).

- 16. A. L. Fripp and L. H. Slack, J. Electrochem. Soc., 120, 145 (1973).